la cpu

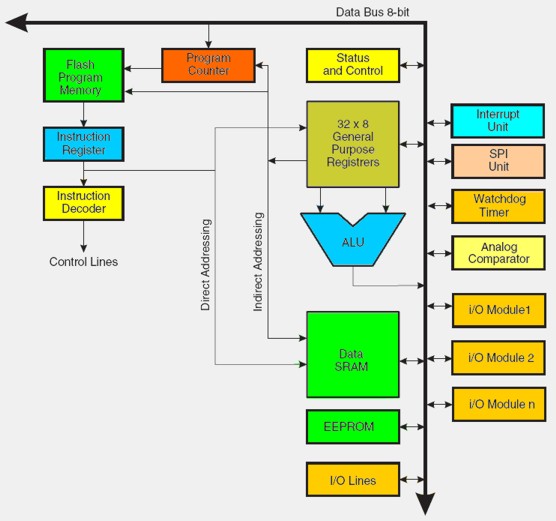

La funció principal de la CPU és assegurar el correcte funcionament del programa en execució i ha de ser capaç d'accedir a memòries, controlar els perifèrics i manejar les interrupcions. La figura 1 mostra un esquema de la CPU.

Figura 1

Els microcontroladors AVR empren una arquitectura Harward amb memòries i busos separats per programes i dades. Les instruccions s'executen amb un nivell de pipelining: quan s'està executant una instrucció es realitza el pre-fetch de la següent instrucció, fet que permet aproximar el rendiment de la CPU a 1 instrucció per cicle de rellotge.

El programa s'emmagatzema en una memòria flash construïda sobre el mateix microcontrolador.

La CPU conté un fitxer amb 32 registres de 8 bits d'accés ràpid que permeten la realització d'operacions amb la UAL en un cicle: en una operació amb la ALU, es treuen els dos operands del fitxer de registres, s'executa l'operació i el resultat s'emmagatzema en un nou registre, en un únic cicle de rellotge.

La UAL suporta operacions aritmètic-lògiques entre registres o amb registre i constant. El registre de Status, que s'actualitza a cada operació de la UAL, conté informació sobre el resultat obtingut.

La major part de les instruccions AVR són de 16 bits. En la memòria del programa s'emmagatzemen instruccions de 16 bits o de 32 bits.

El flux del programa es controla amb instruccions de salt condicionals i incondicionals, i poden adreçar tot l'espai de memòria. En interrupcions i crides a subrutines l'adreça de retorn (Comptador de programes) s'emmagatzema en el stack.

El mòdul d'interrupcions té els registres de control en l'espai d'E/S, i ve controlat per un bit de capacitació d'interrupció. Tota interrupció té un vector d'interrupció en la taula de vectors d'interrupció per adreçar la rutina de servei de la interrupció. La prioritat de la interrupció s'estableix en la posició del vector d¡interrupció dins la taula de vectors.

L'espai de memòria d'E/S conté 64 adreces per accions amb perifèrics de la CPU i inclouen registres de control, comunicació i E/S.

El registre de status: SREG

El registre de status conté 8 bits que guarden la informació sobre el resultat de la darrera oepració de la UAL:

Bit7 - I: Global Interrupt Enable. Bit d'interrupció global que habilita les interrupcions. S'habilita amb la instrucció SEI i es deshabilita amb CLI. Quan està habilitat, es deshabilita en entrar en rutina de servei i es torna a habilita amb RETI, la instrucció de retorn de rutina de servei d'interrupció.Bit6 - T: Bit de còpia. Emprat per copiar i guardar un bit.

Bit5 - H: Half Carry Flag. Emprat en aritmètica BCD.

Bit4 - S: Bit de signe= N orex V.

Bit3 - V: Bit d'overflow de complement a 2.

Bit2 - N: Bit negatiu. Indica un resultat negatiu

Bit1 - Z: Bit de zero. Indica resultat 0 en una operació.

Bit0 - C: Bit de carry. Indica resultat de carry en una operació.

El fitxer de registres

Està constituït per 32 registres de 8 bits.

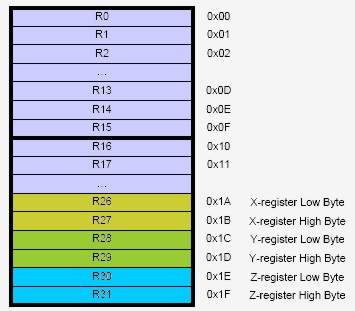

La figura 2 mostra el mapa de memòria ocupat pel fitxer de registres. Es pot observar que cada registre està mapejat en l'espai de memòria de dades. S'ocupa des de l'adreça 0x00 a la 0x1F.

Figura 2

Hi ha 6 registres que, emprats dos a dos, poden ser utilitzats com a tres apuntadors de 16 bits per adreçament indirecte. I un d'aquests registres es pot emprar com a apuntador d'adreces en taules de cerca (look-up table) en la memòria flash per programa. Aquests registres s'anomenen X, Y i Z, i corresponen als registres R27-R26, R29-R28, R31-R30, respectivament.

El stack

El stack és una àrea de memòria per guardar dades temporals i les adreces de retorn en subrutines i rutines de servei d'interrupció.

El stack es posa efectivament en la memòria SRAM, i es troba limitat per la mida d'aquesta memòria i l'ús que se'n faci. El stack s'ha d'inicialitzar en cada programa en la rutina d'inicialització, prèviament a ser utilitzat.

El stack pointer és l'apuntador del stack que referència l'adreça a escriure o llegir quan s'accedeix al stack. El stack pointer es decrementa en u en operacions de posar dades (push) en el stack i s'incrementa en u quan es treuen dades (pop) . Si la dada és la referència a una adreça el decrement/increment és de dos.

interrupcions

AVR tracta diferents fonts d'interrupció que són direccionades a través d'un vector d'interrupció. Els vectors d'interrupció estan localitzats en les adreces baixes de memòria. Així, la primera adreça (la 0x0000) conté el vector d'interrupció del reset. Això és, la primera adreça de memòria conté el vector de Reset, (un salt a) la adreça d'inici del programa. Segueixen a continuació el conjunt de vectors d'interrupció de les següents interrupcions. Quan més baixa és l'adreça, més prioritaria és la interrupció.

Els vectors d'interrupció contenen l'adreça d'execució de la corresponent rutina de servei de la interrupció. Per a què s'activi una interrupció cal tenir habilitat el flag general d'interrupció (flag I del SREG), s'ha de tenir habilitat el bit particular de la interrupció i s'ha de produir l'event concret d'interrupció. El vector d'interrupció de cada interrupció ve especificat en la taula d'interrupcions del microcontrolador. Les interrupcions es deshabiliten quan s'està en la rutina de servei d'una interrupció.

Quan s'entra en una rutina de servei d'interrupció cal guardar (per software) el registre de status i restaurar-lo en sortir de la rutina de servei, ja que aquest no es guarda automàticament. Quan es surt d'una rutina de servei d'interrupció sempre s'executa una instrucció abans de tornar a servir una nova interrupció.

Les instruccions SEI/CLI habiliten/deshabiliten el flag general d'interrupció.

Un programa de configuració típic que inclou els vectors de Reset i d'interrupció tindrà el següent format: Inicialització.