comptadors

El microcontrolador ATmega8 disposa de tres comptadors amb diverses funcionalitats que, conjugades de forma adequada, permeten implementar múltiples aplicacions. Dos comptadors són de 8 bits i el tercer és de 16 bits. Cadascun dels comptadors disposa d'un prescaler per adequar el rellotge del comptador a la seva funcionalitat. Tenen sortida d'overflow i diverses interrupcions. També es disposa de registre de comparació en dos comptadors amb interrupció per comparació. I implementen de forma fàcil la sortida de pols modulat per amplitud de pols.

A continuació s'exposa amb més detall cadascun dels comptadors. Tot i el conjunt de característiques que presenten tenen un funcionament que els permet programa i d'utilitzar de forma simple. Com en els mòduls que s'han vist fins ara, la seva programació passa per actuar sobre el conjunt de registres que personalitzen cada comptador.

El Timer/counter0: TCNT0

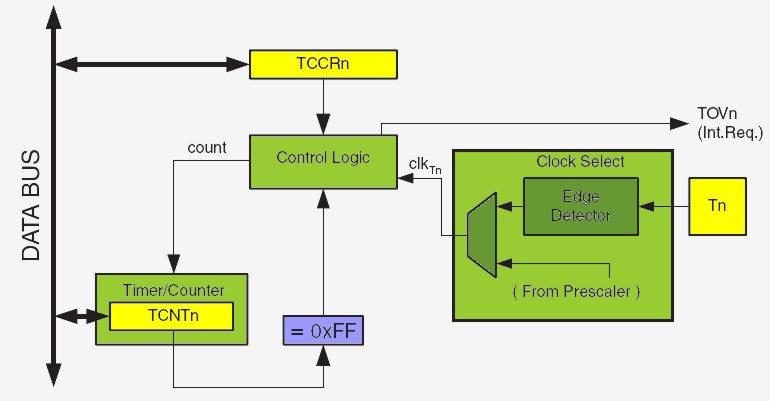

És el comptador més simple. És un comptador genèric de 8 bits que pot emprar-se com a generador de freqüència, amb un prescaler de 10 bits i senyal de rellotge extern si es desitja. El funcionament és molt simple:

El comptador compta a cada pols de rellotge entrant. El rellotge pot ser el propi rellotge del sistema, la sortida de rellotge del prescaler o un event extern (que es captura per un pin dd'entrada/sortida).Quan el comptador canvia del darrer estat (2^8-1 = 255) al primer (0) s'activa el senyal d'overflow. Aquest senyal es desactiva (si no s'empren interrupcions) manualment escrivint un 1 en el mateix flag.

Si el senyal d'interrupció per overflow està activat, la interrupció es produeix en activar-se el senyal d'overflow. En entrar ala rutina de servei de la interrupció es desactiva automàticament el senyal d'overflow. El vector d'interrupció del comptador 0 està posat en 0x009.

El registre comptador és accessible tant per lectura com per escriptura. Per tant, és possible actuar sobre l'estat en el que comença a comptar el comptador.

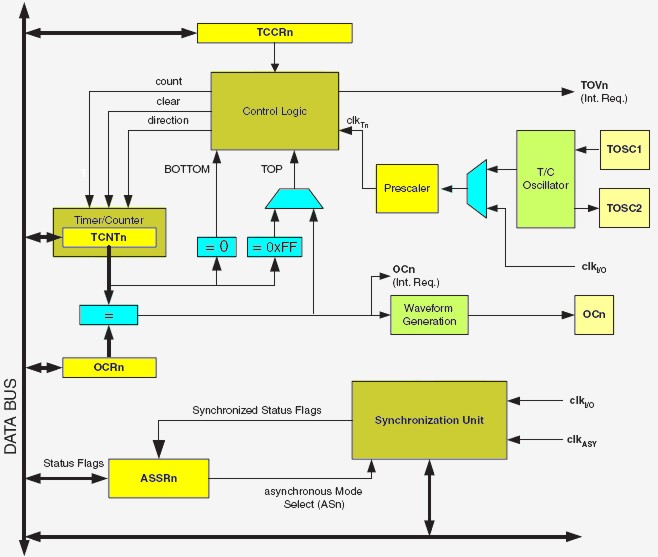

La figura 1 mostra l'arquitectura del comptador. S'hi observen els registres prinicipals i la lògica de control del comptador.

Figura 1. Timer/counter 0

Els registres que actuen sobre el comptador són:

- El registre comptador, TCNT0. És un regsitre de 8 bits que pot ser llegit i escrit. Quan s'escriu, el comptador continua comptant a partir del valor escrit.- El registre de control del comptador, TCCR0. Només s'empren els tres darrers bits (CS02..CS00) que serveixen per seleccionar el rellotge de treball del comptador (veure la taula en el full d'especificacions). Així, per exemple, el valor 0 para el comptador, amb 1 es fa servir el rellotge base clk0 (sense prescaler), amb 2 el rellotge és clk0/8, etc.

- El registre màscara d'interrupció, TIMSK. És el registre d'activació d'interrupció dels comptadors del que, el comptador 0, empra el bit0, TOIE0 (Timer/Counter0 Overflow Interrupt Enable). Quan activat, i amb el flag general d'interrupcions activat, es produeix una interrupció cada cop que el flag d'overflow del comptador (TOV0) es posa a 1.

- El registre de flag's d'interrupció del comptador, TIFR. El comptador 0 empra el bit 0, TOV0. S'activa quan succeeix un overflow. Es desativa en entrar en la rutina de servei d'interrupció per overflow (d'estar activada aquesta interrupció) o escribint un 1 en aquest bit (quan la interrupció no està activada).

- El registre prescaler és un registre intern, comú als comptadors 1 i 0, que només pot ser inicialitzat a zero.

Exemples d'ús

Exemple 1. Generarció d'un pols de període 2 ms amb amplada de pols d' 1 ms en el PORTB.0

Exemple 2. Generació del mateix pols que en el cas anterior, però emprant la interrupció per overflow.

El Timer/counter1: TCNT1

És un comptador de 16 bits. És un comptador complert. Apart de la funció pròpia de comptador disposa de dues unitatas independents de comparació. Té quatre fonts independents d'interrupció: per overflow, dues per comparació i per captura de flanc. Té una unitat de captura d'entrada amb cancel·lació de soroll. Pot generar un pols modulat en amplada variable, etc.

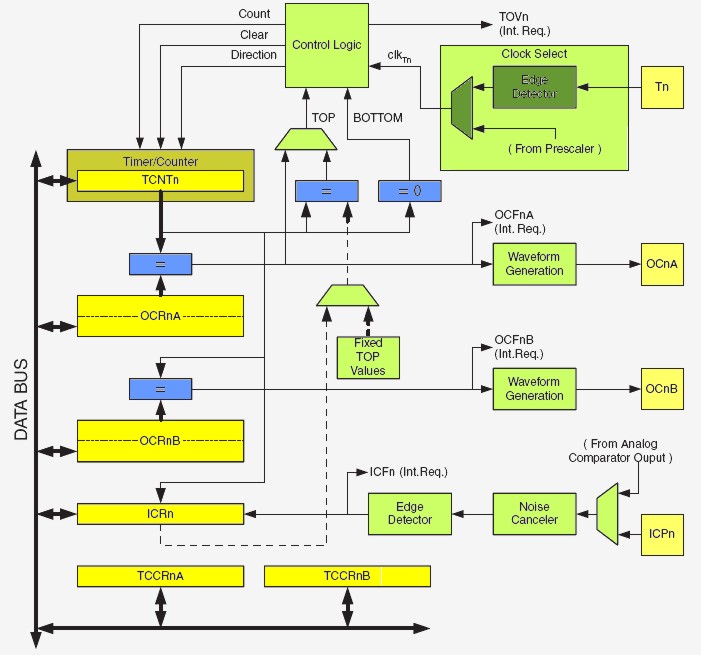

La figura 2 mostra l'arquitectura del comptador 1. S'hi observen clarament els principals registres i la lògica que composen el comptador. A diferència del comptador 0, i donat que es tracta d'un comptador de 16 bits, els regsitres que composen el comptador es composen de dos registres de 8 bits, contenint el byte alt i el byte baix de cada dada. Això implica que s'ha de fer un doble accés quan es llegeix o s'escriuen aquests registres. El mecanisme és el següent:

- Quan s'escriu un registre, primer s'escriu el valor del registre alt, que queda emmagatzemat en un registre temporal. En el moment d'escriure el byte baix també es traspassa el valor del registre temporal en el byte alt.- En la lectura del regsitre el procediment és parecut però a la inversa. Primer s'ha de llegir el byte baix i desprès el byte alt.

Figura 2. El timer/counter 1

Registres i funcionalitats.

Els registres que actuen sobre el comptador són:

- El registre comptador, TCNT1. És un registre de 16 bits que pot ser llegit i escrit que conté al valor del comptador. Convé tenir present que està format pel byte alt TCNT1H i el baix TCNT1L i que qualsevol lectura/escriptura es fa mitjançant aquests dos registres de 8 bits.- Els registres comparadors de sortida A i B, OCR1A/OCR1B. Són registres de 16 bits que contenen valors de comparació amb el valor del comptador. Contínuament es comprova si el comptador arriba al valor emmagatzemat. El resultat permet generar una forma d'ona arbitrària o PWM en els pins de sortida OC1A/OC1B.

Quan el comparador i el comptador coincideixen, en el següent cicle s'activa el flag OCF1A/OCF1B, que és esborrat per software (escrivint-hi un 1), o en entrar en la rutina de servei d'interrupció per comparació (d'estar activada).

L'activació d'interrupció per comparació s'habilita amb el flag OCIE1A/OCIE1B del regsitre TIMSK.

- El registre de captura d'entrada ICR1. És un registre que captura el valor del comptador davant un event extern. L'event es pot produir via el pin d'entrada ICP1 o ve emprant el comparador.

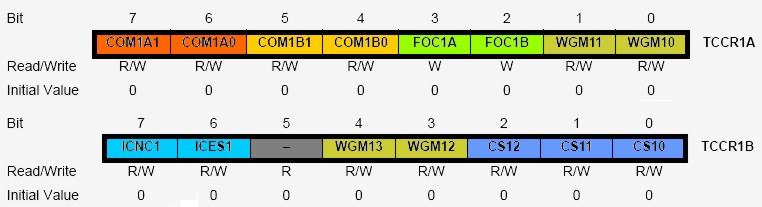

- Els registres de control del comptador, TCCR1A/TCCR1B. Són registres de control d'operació del comptador.

Bits 2-0 del registre TCCR1B, CS12:0. Són els bits de control de rellotge del comptador1. Admeten els funcionaments de rellotge per divisió de la freqüència base per 1, 8, 64, 256, 1024, no funcionament i per rellotge extern (flanc de pujada o baixada) pel pin T1Bits 1-0 del TCCR1A i 4-3 del TCCR1B, WGM13:0. Selecció de mode de funcionament. El comptador pot funcionar en mode normal, Clear on Compare Match, PWM ràpid, de correcció de fase en PWM i de correcció de fase i període en PWM. En els següents paràgrafs s'introdueixen aquests modes de funcionament.

Bits 7-6/5-4 del registre TCCR1A, COM1A1:0/COM1B1:0 - Mode de sortida de comparació del canal A/B. Són els bits de control del funcionament de la sortida segons el mode de funcionament del comptador.

Bit 7 del TCCR1B, ICNC1 - Bit de cancel·lació de soroll del comptador 1. Bit d'acticació de filtre per reduir el soroll en el pin ICP1.

Bit 6 del TCCR1B, ICES1 - Bit de d'especificació de flanc de captura del pin ICP1 del comptador 1.

Bits 3-2 del TCCR1A, FOC1A, FOC1B - Forcen la comparació del comptador. Donat que només actuen en mode no PWM i no està garantit el seu ús en posteriors versions del microcontrolador és millor no emprar-los.- El registre màscara d'interrupció, TIMSK. Com en el comptador 0 és el registre d'activació d'interrupció dels comptadors. Els bits que afecten al comptador1 són:

Bit 2 - T0IE1. Bit d'habilitació d'interrupció per overflow del comptador.

Bit 3- OCIE1A. Bit d'habilitació d'interrupció per comparació amb el registre A.

Bit 4- OCIE1B. Bit d'habilitació d'interrupció per comparació amb el registre B.

Bit 5 - TICIE1. Bit d'habilitació d'interrupció per captura externa.- El registre de flag's d'interrupció del comptador, TIFR. És el registre de status del què passa en el comptador, comú als altres comptadors. Conté els següents flags referents al comptador 1:

Bit 2 - TOV1. És el flag d'overflow del comptador.

Bit 3- OCF1B. És el flag de comparació amb el registre B.

Bit 4- OCF1A. És el flag de comparació amb el registre A.

Bit 5- ICF1. És el flag de captura pel pin ICP1.

Modes de funcionament

El comptador1 té diversos modes de funcionament controlats pels bits WGM13:0 que estan totalment especificats en el full d'especificacions del microcontrolador.

Els modes més importants són:

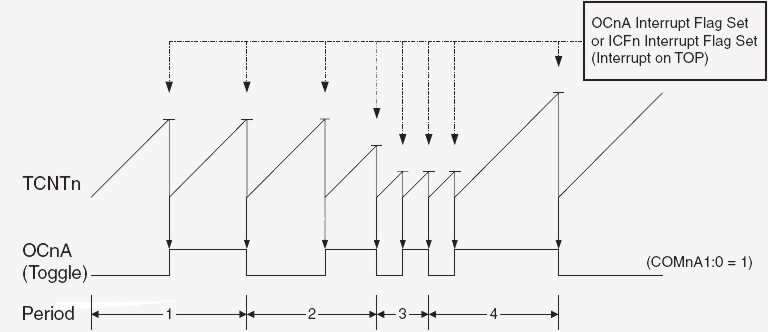

- El mode normal. És el mode simple d'ús del comptador. Es selecciona posant WGM13:0 = 0. El comptador compta en mode ascendent fins que es produeix overflow, i aquest s'ha d'esborrar manualment (de no emprar interrupció per overflow). Es poden emprar les unitats de comparació per generar interrupcions a temps determinats.- Inicialització de comptador sobre comparació (mode CTC). El comptador es posa a 0 quan el valor del comptador s'iguala amb OCR1A (WGM13:0=4) o ICR1 (WGM13:0=12). Es pot generar una interrupció cada cop que s'arriba al valor de compteig, valor TOP, emprant OCF1A o ICF1.

Aquest mode pot emprar-se com a generador d'ones si es posa la sortida en mode de commutació per comparació de sortida (COM1A1:0=1).

El valor de comparació és un valor fix (quan WGM13:0 val 5, 6, o 7), el valor en ICR1 (mode 14) o el valor del comparador OCR1A (valor 15). Quan el comptador arriba a un d'aquests valors, en el cicle següent es posa a 0.

La figura 3 mostra el funcionament del comptador. Cada cop que arriba al valor TOP el comptador reinicia el seu compteig a BOTTOM.

Figura 3. Funcionament del comptador en mode Clear on Compare Match (CTC)

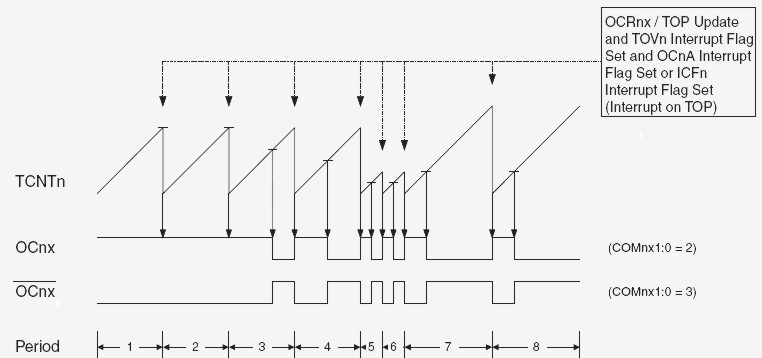

- Mode Modulació en amplitud de pols o PWM ràpid. El comparador admet diferents modes PWM segons WGM13:0 estigui en 5, 6, 7, 14 o 15. Difereix d'altres modes PWM per què es realitza en mode de pendent simple: el comptador compta d'un valor BOTTOM a un TOP, tornant a començar en el BOTTOM.

En el mode de no inversió en Comparació per sortida (COM1x1:0=2), la sortida de comparació OC1A/OC1B es posa a 1 en la comparació i torna a 0 quan s'arriba al valor TOP. En el mode d'inversió (COM1x1:0=3) el funcionament de la sortida funciona a la inversa.

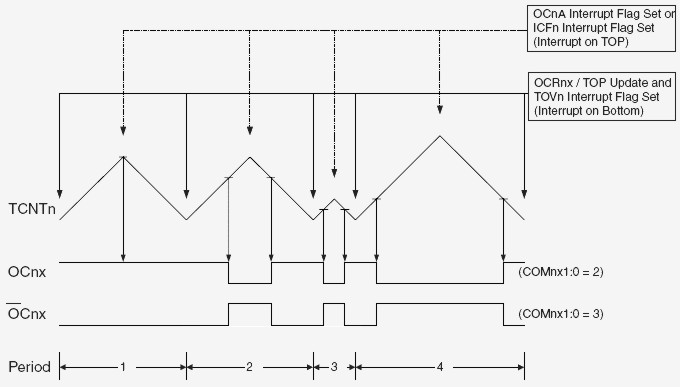

El funcionament es mostra en la figura 4. En aquest cas la sortida fa un doble canvi de valor en un període: primer canvia quan el comptador arriba al valor de comparació i després ho torna a fer en arribar al valor TOP.

Figura 4. Funcionament en mode Fast PWM. Les marques horitzontals indiquen comparacions entre el comptador i el comparador

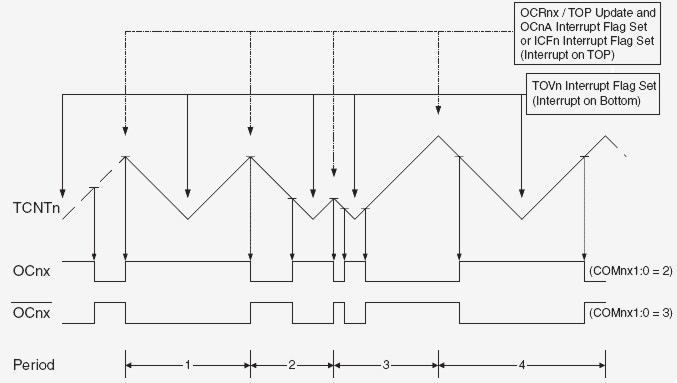

- Mode PWM amb correcció de fase (WGM13:0 estigui en 1, 2, 3, 10 o 11). És un mode PWM d'alta resolució, basat en operació de doble pendent. El comptador va comptant de BOTTOM a TOP i de TOP a BOTTOM. La sortida OC1A/OC1B es posa a 1 (suposant mode no invertit, sino va a la inversa) quan compta amunt i arriba al valor de comparació i torna a 0 quan el comptador compta avall i torna a arribar al valor de comparació.

El valor de comparació és un valor fix (modes WGM13:0 as 1, 2 o 3), el valor en ICR1 (mode 10) o el valor del comparador OCR1A (valor 11), i representa el valor TOP del comptador. Donar que s'arriba al valor de comparació es genera una interrupció OC1x. La interrupció per OVF es generarà quan s'arribi al valor BOTTOM.

El funcionament es mostra en la figura 5. Es veu com en aquest cas la sortida fa un doble canvi de valor en un període: primer canvia quan el comptador arriba al valor de comparació (que esdevé valor TOP) i després ho torna a fer en arribar al valor de comparació.

Figura 5. Funcionament en mode Phase Correct PWM. Les marques horitzontals indiquen comparacions entre el comptador i el comparador

En aquest mode s'ha d'anar en compta en el moment d'actualitzar el valor TOP, ja que s'ha d'assegurar que el nou valor TOP és superior al del valor emmagatzemat en els registres. De no complir-se hi poden haver fallades de detecció.

Quan el valor TOP es canvia mentre el comtador està funcionant sol ser més recomanable emprar el mode PWM amb correcció de fase i freqüència.

- Mode PWM amb correcció de fase i freqüència (WGM13:0 estigui en 8 o 9). Basat en doble pendent, és un mode de correcció de fase i freqüència.

El comptador compta de BOTTOM a TOP i de TOP a BOTTOM. La sortida de comparació OC1x s'esborra en arribar TCNT1 al valor de comparació OCR1x en ascenció i es posa en a 1 en comptar avall (en mode de no inversió, si no va al revés).

A diferència del cas anterior els valors de comparació s'actualitzen en arribar al valor de BOTTOM. Això fa que el temps de pujada i de baixada siguin simètrics.

El funcionament es mostra en la figura 6.

Figura 6. Funcionament en mode Phase and Frequency Correct PWM. Les marques horitzontals indiquen comparacions entre el comptador i el comparador

Exemple d'ús

Exemple 3. Control d'un servomotor.