Mòduls analògic/digitals

El microcontrolador ATmega8 disposa de dos

mòduls d'entrada analògics: un comparador i un mòdul

conversor analògic-digital que admet fins a 8 entrades diferents

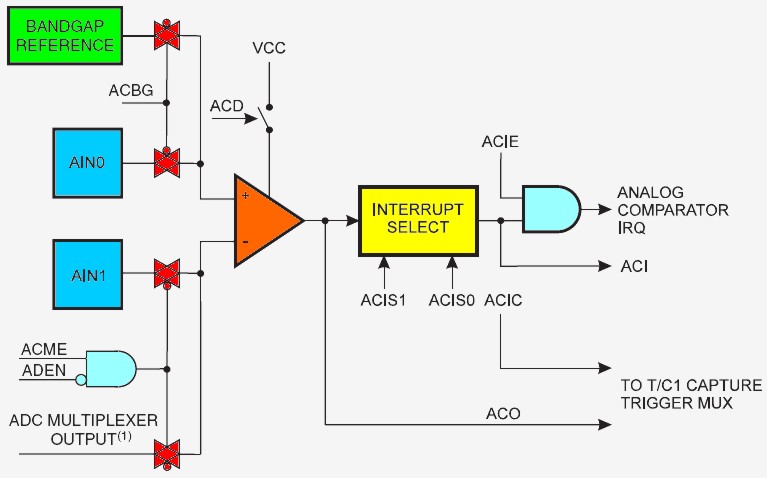

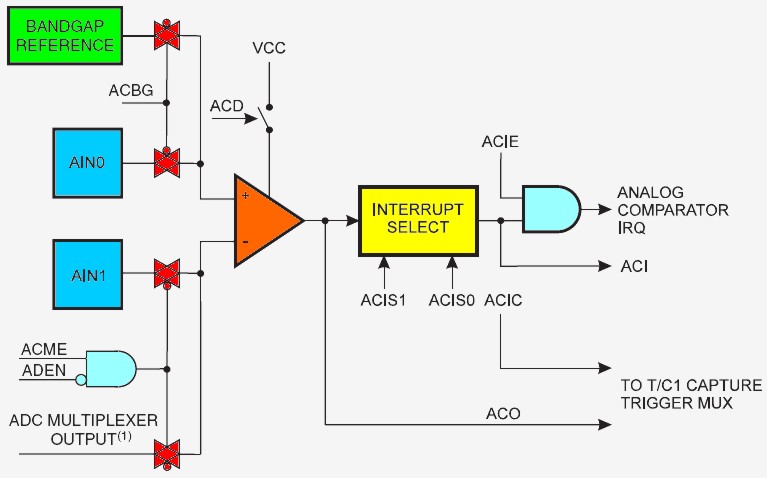

comparador

El funcionament del comparador és simple.

Compara la diferència de potencial que hi ha entre les entrades AIN0

i AIN1. Si és positiva la sortida AC0 és un 1-lògic.

En cas contrari es té un 0-lògic.

Apart d'aquest funcionament bàsic,

- El comparador admet com a entrada per

AIN0 una tensió de referència fixa donada pel microcontrolador

- L'entrada AIN1 pot ser una de les entrades

multiplexades que entren al conversor analògic-digital.

- Es pot emprar la sortida de comparació

com a entrada de rellotge pel Timer1.

- I disposa d'una unitat de control d'interrupció

que es pot programar per flanc o per canvi de nivell.

Figura 1. Arquitectura del comparador

Els registres que controlen el funcionament

del comparador són:

- El registre d'E/S de funcions especials,

SFIOR. El bit que afecta al comparador és el:

Bit 3 - ACME. Quan s'activa permet,

amb la cooperació del bit ADEN, que l'entrada AIN0 provingui d'un dels

bits del conversor analògic-digital. Quan s'empra el multiplexor del

ADC per a aquest fi, s'ha de deshabilitar del ADC.

- Registre de status i control del comparador,

ACSR. Com en el comptador 0 és el registre d'activació

d'interrupció dels comptadors. Els bits que afecten al comptador1 són:

Bit 1:0 - ACIS1:0. Selecció

del mode d'interrupció del comparador, per nivell o per flanc.

Bit 2 - ACIC. Habilita que el Timer1 pugui ser controlat per la sortida del

comparador.

Bit 3- ACIE. Bit d'habilitació d'interrupció del comparador.

Bit 4- ACI. Bit que s'activa en produir-se la interrupció sobre el

comparador. S'esborra en entrar en la rutina d'interrupció o escribint'hi

un 1.

Bit 5 - ACO. Sortida sincronitzada del comparador.

Bit 6 - ACBG. Quan està activat la comparació es fa sobre el

valor de bandgap connectat en l'entrada positiva.

Bit 7 - ACD. Bit d'habilitació del comparador. Quan no s'empra el comparador

convé que estigui desactivat, ja que redueix el consum. Per altra part,

qualsevol canvi en aquest bit s'ha de fer amb el bit d'interrupció

del comparador ACIE aturat per evitar que provoqui cap interrupció.

adc's

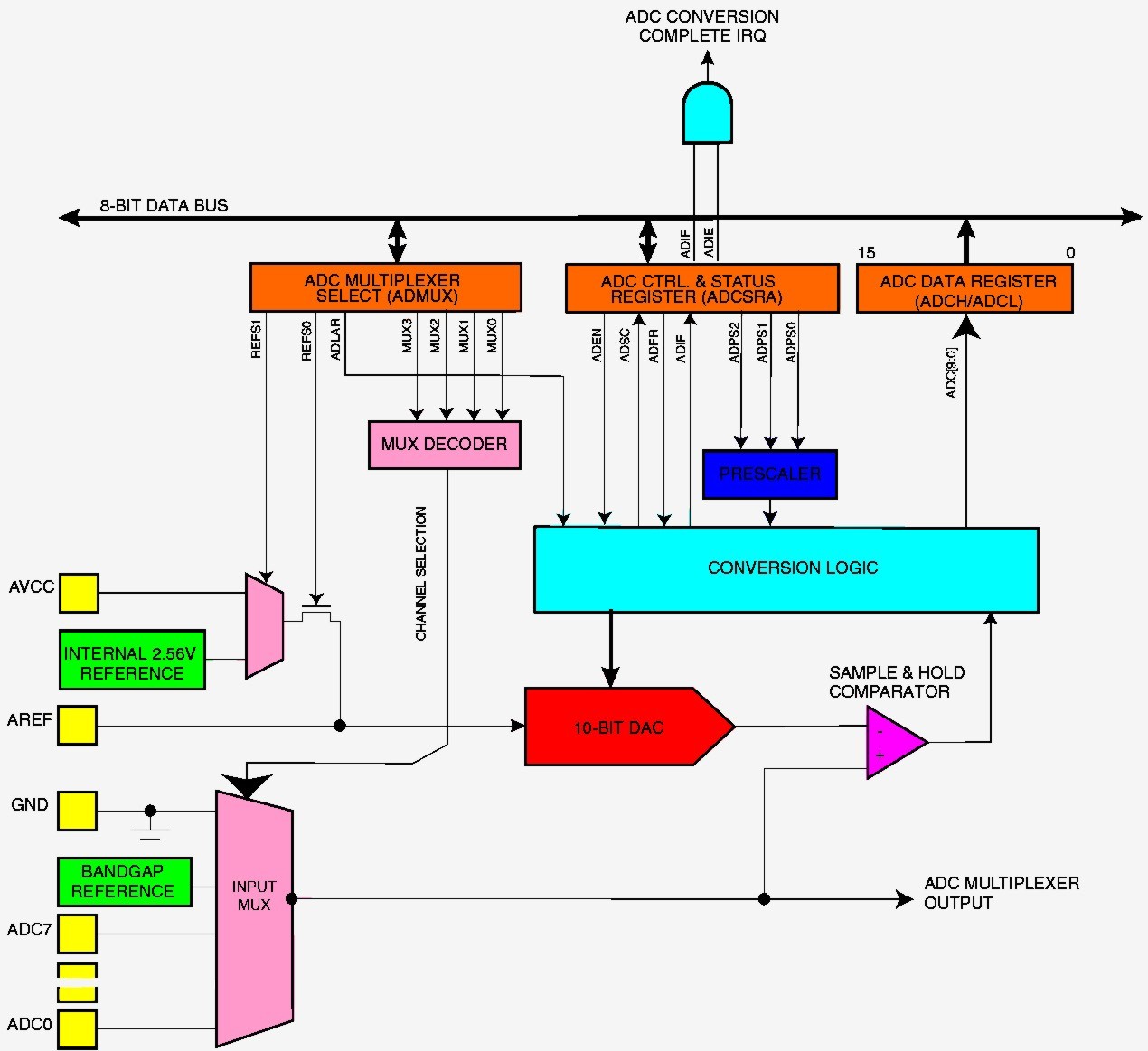

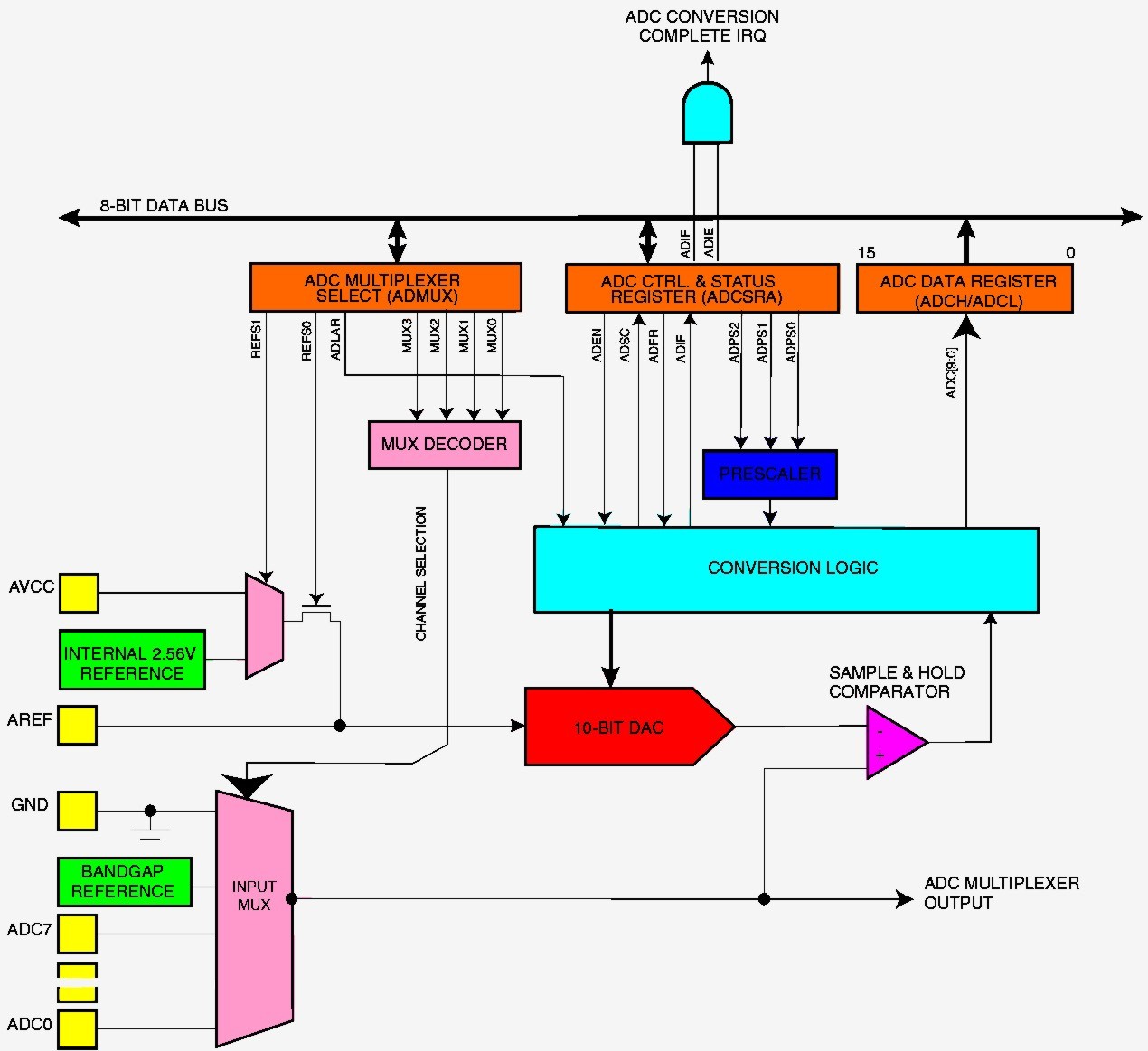

El microcontrolador ATmega8 conté un

conversor analògic/digital de 10 bits per aproximacions successives

connectat a 10 pins d'entrada multiplexats que admet el senyal provinent,

per multiplexació, de fins a 8 pins. La figura 2 mostra l'arquitectura

del conversor. El voltatge de referència intern pot ser de 2.56V o

la tenció d'alimentació analògica AVcc.

Figura 2. Arquitectura del ADC

El valor de conversió mínim

és el terra i el màxim és la tensió de referència

AREF menys 1LSB. La tensió de referència pot ser externa o (es

pot connectar internament) AVcc o els 2.56V interns.

Quan no s'empra el conversor convé

deixar-lo deshabilitat (el bit ADEN a 0) per evitar consum innecessari.

La conversió és de 10 bits,

el que implica (donat que el bus és de 8 bits) una doble lectura. Però,

si la precisió que es necessita no és major de 8 bits, aleshores

es pot ajustar a l'esquerra i llegir el registre alt ADCH, obviant els bit

menys significatius.

La conversió del ADC s'inicia posant

un 1 en el bit ADCS, i continua mentre aquest bit sigui 1. Si s'empren interrupcions,

la interrupció del ADC indica que la conversió ha acabat.

El conversor pot funcionar en mode de conversió

única (sota petició de conversió) o en mode lliure (el

ADC va convertint contínauament l'entrada que arriba). Per a aconseguir

una resolució màxima la freqüència del rellotge

del ADC ha d'estar entre 50KHz i 200KHz. Una conversió normal dura

13 cicles de rellotge del conversor (a excepció de la primera conversió,

en què inicialitza la circuiteria de conversió que en dura 25).

El resultat de conversió ve determinat

per ADC = Vin·1024/Vref, essent Vin el voltatge provinent del pin d'entrada

seleccionat i Vref la tensió de referència seleccionada. ADC

pren, per tant, un valor entre 0x000 i 0x3FF.

Els registres que controlen el funcionament

del conversor són:

- El registre de selecció del

multiplexor ADC, ADMUX.

Bit 3:0 - MUX3:0. Selecció

de l'entrada del conversor ADC

Bit 5 - ADLAR. Bit d'ajustament a l'esquerra del resultat

Bit 7:6 - REFS1:0. Seleccionen el voltatge de referència: AREF, AVcc

o els 2.56V interns

- Registre A de status i control del

conversor, ADCSRA.

Bit 2:0 - ADPS2:0. Bits de selecció

del prescaler. Factors de de divisió de 2 a 128

Bit 3- ADIE. Bit d'habilitació d'interrupció del conversor

Bit 4- ADIF. Bit que s'activa en acabar-se la conversió. S'activa la

interrupció del ADC si està activada. S'esborra en entrar en

la rutina d'interrupció o escribint'hi un 1

Bit 5 - ADFR. Activat indica mode d'operació lliure del conversor

Bit 6 - ADSC. Bit d'inici de conversió. En conversor simple es fa una

conversió quan es posa a 1. En mode lliure indica que comencen les

conversions. Torna a 0 un cop s'ha acabat la conversió

Bit 7 - ADEN. Bit d'habilitació del conversor. Quan no s'empra el conversor

convé que estigui desactivat, ja que redueix el consum

- Registre de dades del conversor, ADCH,

ADCL. És el registre de sortida de conversió. Quan

està ajustat a l'esquerra el valor es troba en els bits 15:6. Si no

, el resultat queda en 9:0.

El codi exempleADC

mostra un codi d'exemple d'ús del ADC.